MSRA 读博五年(一)从小白到第一篇 SIGCOMM

长文预警:《MSRA 读博五年》系列之一,约 12000 字,未完待续……

2021 年 7 月 31 日,ACM 中国图灵大会上,我站在主席台上等待 ACM 中国优秀博士学位论文奖,没想到走上台来为我颁奖的是包校长,我的双腿不由自主地有些颤抖。这是我唯一一次近距离见到包校长。包校长高兴地说,看到获奖人中有我们中科大的,说明中科大也是可以培养大师的,希望以后你们能够成为大师,报效祖国,回归母校。

颁奖典礼的主持人刘云浩教授让我们说说博士论文的标题和导师,我脱口而出,《基于可编程网卡的高性能数据中心系统》,导师是中科大的陈恩红教授和微软的张霖涛博士,还要特别感谢华为的谭焜博士。我能清楚地记住博士论文的标题,它就挂在自己的主页上。在公司里,经常有人给我发私信,问我你就是某某论文的作者吗?我就不好意思地说,是的……

很多人也许认为,我是那种一心学习的博士,其实我的博士生活比很多人想象的有趣很多,真应了 MSRA(微软亚洲研究院)这句格言 “Work hard, play harder”。

研究小白

联合培养

MSRA(微软亚洲研究院)跟国内的多所高校有联合培养博士生项目。其中,跟中科大的联合培养项目已经持续多年。大三下学期,MSRA 到学校面试几十位候选人,从中选出十几位学生到 MSRA 进行暑期实习和大四一年的实习,并在暑期实习结束后确定下来大约 7 位学生成为联合培养博士。这些联合培养博士将在中科大完成第一年的硕博课程,而后面四年将在北京的 MSRA 进行学术研究,最后取得中科大的博士学位。

MSRA 选拔联合培养博士的要求是所谓 “三好” 学生:数学好、编程好、态度好。这个规矩据说是前院长沈向洋博士定下来的。我本科因为整天在少年班学院机房和 LUG 活动室倒腾各种 Linux 网络服务,不怎么好好学习,成绩自然也不好看,GPA 只有 3.4(满绩 4.3),其中数学分析(二)还挂过科。面试官当时就问我,数学成绩怎么这么差。大概是我高中曾经在编程竞赛(NOI)中得过奖,简历上又有很多在LUG搞的网络服务项目,最后我竟然被联合培养博士项目录用了。其他被联合培养项目录用的同学 GPA 都起码是 3.7,大部分都是 3.8 以上的大神。

初入 MSRA

还记得大三升大四那个暑假(2013 年 7 月),我第一天来到 MSRA,就被优越的办公环境震撼了。茶水间有免费的饮料、酸奶和水果,办公位宽敞明亮,网速又快又可以上 Google,服务器配置都是顶级的,当时就已经是 128 GB 内存了。我虽然没有进过学校的实验室,但在少院机房里面搞 Freeshell(基于 OpenVZ 的容器托管服务),上千个容器就只是挤在一个 7 节点的小集群上,每个物理节点只有 16 GB 内存,整个集群的内存容量还不如 MSRA 的一台服务器,而我们组有几十台这样的服务器。

上图:学校少院机房的服务器,上面一层土

上图:学校少院机房的服务器,上面一层土

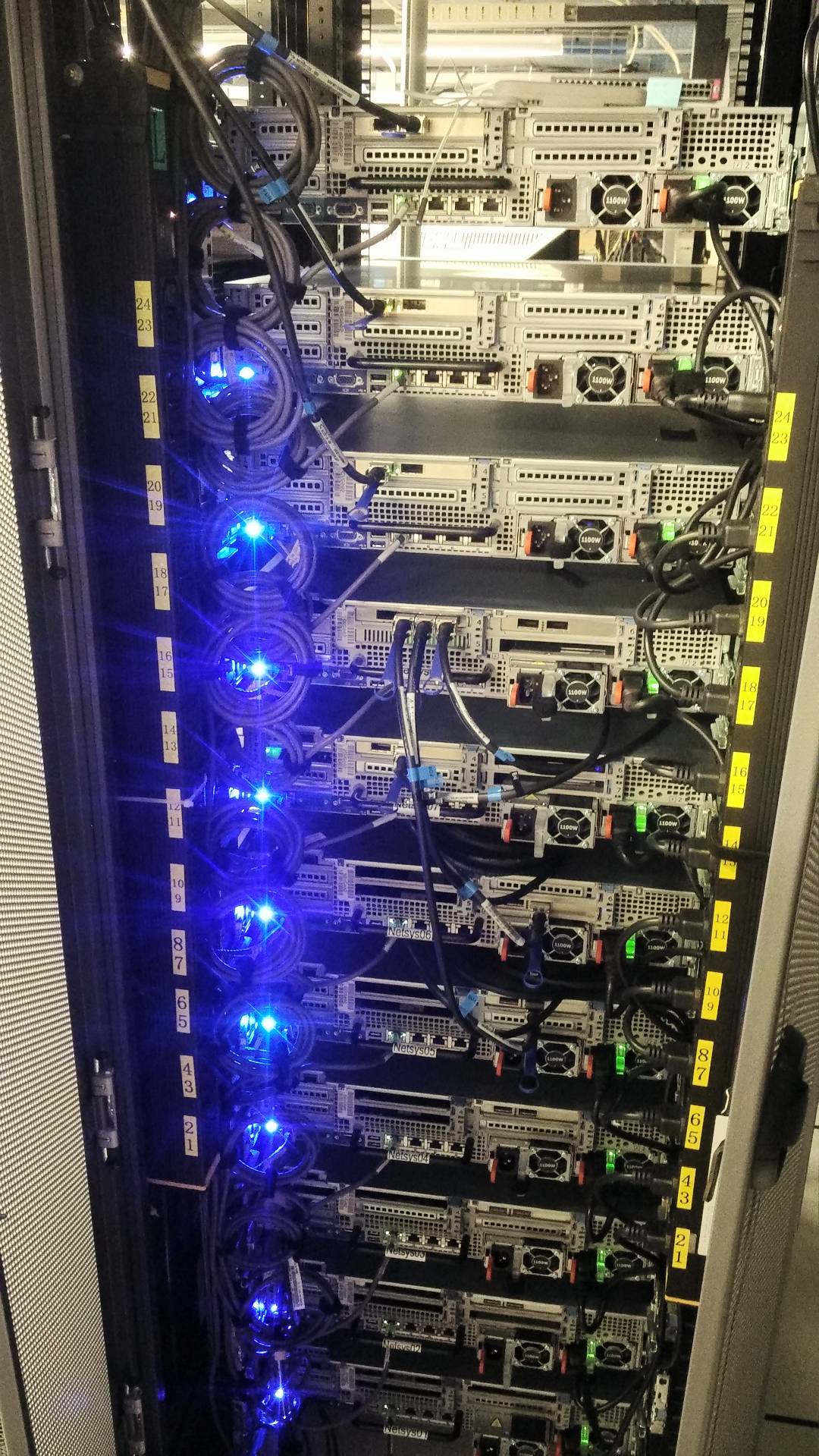

上图:MSRA 的服务器,明显高端很多

上图:MSRA 的服务器,明显高端很多

网络系统组的主管张永光老师把我分配给谭焜导师,谭博就召集我们开会,讲研究应该怎么做。让我印象最深的是,他说需要慢慢学一些管理,我就有点纳闷,做研究为什么需要学管理呢?后来我才明白,做研究需要跟团队中的其他成员合作;当跨过初级研究员这个门槛后,更是需要带领其他研究员一起合作,像谭博这样的资深研究员,需要为整个团队谋划方向、争取资源、招贤纳士、选用育留,都是非常难的。当然,这是后话了,我当时还不知道什么叫研究,更不知道什么叫系统研究。

大四这一年,我开始参与高性能数据中心网络的研究,才明白我在学校倒腾的这些系统性能都是战五渣。我还记得我给少院机房从百兆网络升级到千兆网络,扯了很多根超五类线、六类线,把几台百兆交换机换成了千兆;而在 2013 年的 MSRA 网络系统组,服务器的网络都是 40 Gbps 的,足足快了 40 倍。在这样高速的网络下,主机 TCP/IP 协议栈的性能成为了瓶颈,需要用 DPDK 这样的用户态协议栈技术来加速。那一年,我们集结全组的力量,做了一个基于 DPDK 的高性能网络处理框架,2014 年 1 月投到了 SIGCOMM 上,却遗憾地被拒了。我在这个项目中主要负责做实验,当时从组里继承来的 gnuplot 模板一直用到了博士毕业。

虽然这个项目并没有发表学术论文,但我从中尝到了做研究的甜头。本科的时候,以为研究就是推公式,很无聊,也没什么用。经过半年的实习,我才明白网络和系统的研究是在解决现实世界中存在的问题,虽然不一定能够直接落地到产品,但对学术界和工业界的其他人是有指导意义的。因此,我放弃了创业、直接工作和出国读博,选择了中科大的 MSRA 联合培养博士。

都说 deadline 是第一生产力,每周的组会是大家最大的动力。每次组会,都要有一名同学做比较正式的分享,大家轮流着来;其余每名同学也要同步下最新的状态。在 MSRA,书面的邮件、PPT 都要求是英文的,平时讨论自然是中文,但是正式的分享报告也要求用英文。学术论文和技术资料更不必说,都是英文的。正是因此,在 MSRA 的同学们英语水平一般都有一些自然的提高,比如我在 2018 年纯粹是为了好玩,裸考过一次托福,得分 103,强项是阅读和听力,弱项是口语和写作。大多数出国的 MSRA 同学们是认真准备过的,比我考得高。

上图:MSRA 的服务器,用的都是 40G 的网络

上图:MSRA 的服务器,用的都是 40G 的网络

后来我才知道,这样好的实验平台并不是 MSRA 每个组都有的,当时国内其他高校的实验室更是难以望其项背。谭博不仅顺应微软 “Cloud + Client”(云+端)的战略,将无线与网络组的研究重点调整到了数据中心网络上,确立了基于 FPGA 这样一个有独特平台优势的研究方向,还与总部的 Azure Networking 和 Catapult 产品团队深入合作,获取到服务器、交换机、网卡、FPGA 等硬件资源,搭建了世界领先的数据中心网络和可编程网卡实验平台。32 台服务器、10 台交换机组成了一个三层数据中心网络的典型拓扑,由 2 个 Spine、4 个 Leaf、4 个 ToR 交换机组成,每个机柜内有 8 台服务器。

上图:孟梦学姐和贺同师兄借用大会议室调试 SORA 软件无线电系统,无线和网络是我们组当时的两大方向

上图:孟梦学姐和贺同师兄借用大会议室调试 SORA 软件无线电系统,无线和网络是我们组当时的两大方向

我的第一个研究项目

属于我自己的第一个研究项目是网络交换机的编程。我们当时有 Broadcom 交换机芯片的 spec 和 SDK,可以配置交换机表项。Guohan 还做了一个操作系统镜像,烧到数据中心的交换机里面,交换机就变成了一个标准的 Linux 系统,加上 PXE 网络启动,交换机配置起来就非常方便了。我到现在都跟崇拜 Guohan,不知道他怎么搞出这个操作系统镜像的。

谭博发现,交换机升级或者软件故障就会重启,重启的时间一般很长,柜顶交换机一重启,机架内的所有服务器就会有长达几分钟的网络中断,这对服务的高可用性是很大的威胁。当时其他关于交换机高可用性的研究大多需要增加冗余链路和冗余设备,这会带来较高的成本。而交换机厂商提出的 “Warm Reboot” 解决方案只是缩短了操作系统重启的时间,路由器芯片仍然需要重新初始化。

我们进一步探究,发现软件故障很多时候是不同种类的路由协议所下发的转发规则发生了冲突。为此,我们的想法是对交换机的转发能力进行一定程度的虚拟化,把不同路由协议从逻辑上隔离开来,由中心化的同步服务来解决路由协议间的配置冲突,减少逻辑错误。另一方面,交换机故障或升级时需要重启整个交换机,是因为交换机软件是一个整体,进程一旦重启,路由信息就丢失了。我们采用解耦的思路,把交换机软件的功能拆分为简单而稳定的轻量级路由信息库和相对复杂的同步服务,从而避免单点故障,并且在一个组件升级的时候不会影响其他组件。

这就是我的本科毕业论文,《SDN路由器的容错软件架构》。当时我的好友郭家华和我都在 MSRA 无线与网络组实习,谭博让我们两个合作这个项目。说来也巧,郭家华是我在中科大认识的第一位新同学。我坐了一夜火车来到少院寝室楼下,等了不一会儿,郭家华就也拖着行李箱来了。我高中的时候几乎没有接触过 Linux,但他已经对 Linux 驾轻就熟。因此,在科大期间,我就总是向郭家华请教 Linux 方面的知识,从少院机房到 LUG,课程作业也经常是我们一起做。

在这个路由器容错软件架构的项目中,我负责同步服务,郭家华负责轻量级路由信息库。我们两个的本科毕业设计分别是这个项目的两个方面。我所做的同步服务主要负责解决多个客户端(分别负责不同类型的路由协议)间的配置冲突,并且确保算法的确定性,即故障恢复后再次针对相同的客户端配置(可能以不同的次序到达)解决冲突的最终结果相同。此外,还需要调用交换机芯片 SDK 的接口,进行增量同步。

当时我们还考虑了为什么要自己做一个定制化的路由信息库,而不能直接用 MySQL、Redis 等。这是由于模糊匹配表中的条目是有序的,顺序代表优先级。而关系数据库中的表都是无序表,因此不能直接采用关系数据库。如果简单地把模糊匹配规则的顺序作为关系数据库中的一个额外域段,则在指定位置插入模糊匹配规则后,其后条目的顺序都需要修改,代价较高。Redis 这种键值数据库所提供的抽象就更不适合路由器的查找表了。

第一次尝试写论文

本科毕业之后,我从学校拿到了导师同意函,可以利用本科毕业到研究生入学这段时间再做一段暑期实习。

这时,还是沿着交换机芯片的表项配置这条路,谭博有了一个更大的想法。交换机芯片的表项非常复杂,一个交换机有很多张表,每张表所能匹配的数据报文头上的域段都不相同,不同种类的交换机芯片的表项配置又是大相径庭。当时,SDN(软件定义网络)的概念刚刚开始火起来,大家都想用一种统一的描述语言来配置数据中心里面的路由、转发、防火墙、报文修改等策略。谭博自然就想到,是否可以用一种统一的描述语言来对不同种类的交换机芯片进行抽象呢?

我们花了两个月的时间,设计了一种将 OpenFlow 的通用表结构映射到交换机的特定表结构的算法,但是实际中仍然有比较大的局限。2014 年 9 月 17 日,老板结束了一个月的国际会议返回北京,我汇报了一个月来的进展,虽然我对自己的成果还很不满意,他说我的模型相比一个月前有了很大的进步。9 月 18 日是 NSDI 摘要注册的 deadline,那天晚上,谭博跟我在办公室里一起熬到了凌晨三四点,我在把算法和证明整理成几页 LaTeX 文件,谭博看了,说肯定是赶不上 7 天后的论文 deadline 了。有了之前投稿 SIGCOMM 的经验,我深知一篇系统论文从算法到实现,再到成文需要多少工作量。19 日,我就踏上了回学校的火车,开始研一的课程。

回学校后,我跟学校的创业团队还没有完全中断联系,还曾打电话向谭博请教无线方面的问题。谭博说,要专注于我自己的科研。不过,在学校的这一年,我早就把交换机芯片的表项配置这个研究项目忘到九霄云外了,回学校两个月都没有主动联系导师,这个项目就算是黄了。谭博说,这一年你就在学校好好上课,享受生活就行了,多读读经典论文。

上图:我在研一期间给谭博发的进展汇报邮件

上图:我在研一期间给谭博发的进展汇报邮件

在随后的一两年里,SIGCOMM 等顶级会议上果然有其他论文做了这个问题,理论上的难题果然还是如我预想的那样难以解决,但是实际的路由配置也许没有这么复杂。如果我当时更投入一些,是不是有可能论文就是我发的呢?不过,我觉得由于我没有编程语言理论方面的背景,相比别人的论文,在理论深度上还是略逊一筹,SIGCOMM 的中稿率只有 10%~20%,我的论文未必能在残酷的竞争中存活。

后来我才发现,新研究生最喜欢做的就是 “改进式” 的工作,觉得别人的工作有这样那样的问题(比如性能太差),我可以设计一个更好的算法来解决这个问题。在算法设计方面,往往没有 “精巧” 的感觉,而只是比别人多考虑了几个因素,或者 A+B 形式地把两个或多个相关工作合并起来。这样的文章是很难中顶会的。但这确实是发水会、增加论文数量的一条捷径。顶会论文往往需要新的场景、新的问题、新的方法。我作为研究小白,一开始也险些掉进这个坑里,幸亏谭博及时把我拉出来了。

在研究生的第一年,按照联合培养博士生项目的规划,我把学校里硕士和博士阶段需要上的课都上了。我还在继续维护和改进科大 LUG(Linux User Group)的多项网络服务,还跟当时的女朋友和我的室友一起开发了科大的评课社区。

我虽然技术还算可以,但是软件工程的观念比较差。几乎每天都有人来给我们报 bug 或者提新的需求,我经常是直接在生产服务器上修改代码,改一个功能的时候把其他的又给搞坏了。当时 jameszhang 老师就说,我做的东西缺乏版本的概念。现在看来,也缺乏自动化测试的概念,每次改完了运行一下感觉没问题就上线了,这样就很容易影响到其他的功能。评课社区用的 Flask 框架是我的室友选的,这个框架历经 7 年仍然没有腐化,很容易支撑新功能的开发;而我本科时没有基于框架自己写的代码很快就变得难以维护。

上图:jameszhang 老师给我们讲解中科大校园网络架构,网络的稳定运行和持续演进需要好的架构支撑

上图:jameszhang 老师给我们讲解中科大校园网络架构,网络的稳定运行和持续演进需要好的架构支撑

在一代又一代 LUG 小伙伴们的努力下,越来越多优秀的小伙伴们加入了 LUG,使 LUG 成为校内计算机技术精英汇聚的社团,其中又有很多同学后续加入了 MSRA 的联合培养项目。在 LUG 开发的网络服务和评课社区也是我在科大期间最引以为豪的事情。

在少院技术部和 LUG 维护服务器的经历,最直接的效果是让我说话的声音很大,办公室里经常有人让我开会的声音小点。这是因为机房里面的噪声高达 80 多分贝,声音小了听不清。其次就是让我对 Linux 和网络比较了解,做系统研究感觉比较舒服。

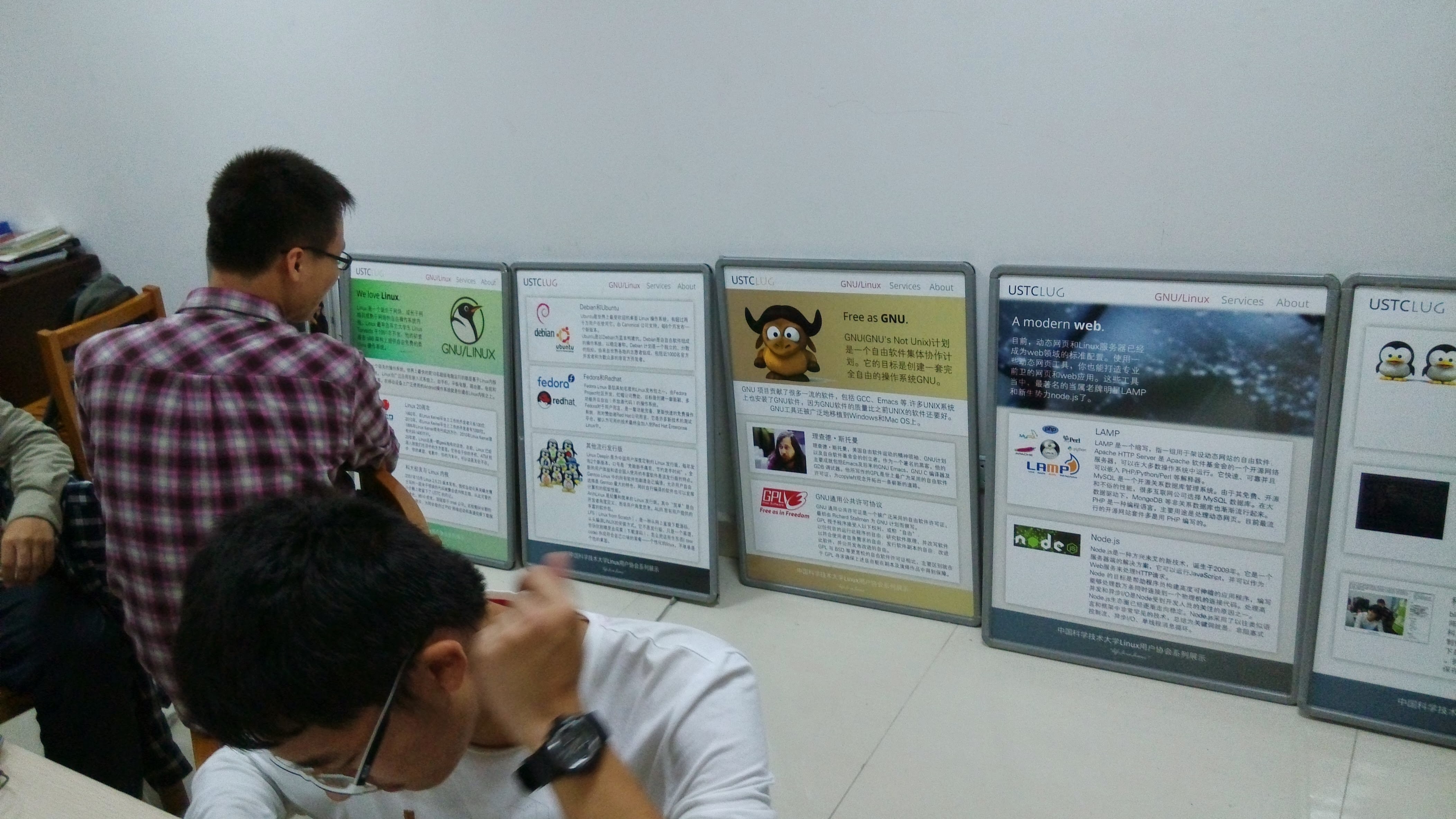

上图:USTC LUG 活动室一角,这是李喵喵做的展板

上图:USTC LUG 活动室一角,这是李喵喵做的展板

我的第一篇 SIGCOMM 论文

我的第一篇论文是谭博手把手带着写的。 这不仅仅是一篇论文,也是当年整个网络组的旗舰项目,很多研究员和实习生都投入到了这个项目中来。论贡献,这个项目的第一作者更应该是谭博而不是我。

FPGA 编程的挑战

早在 2015 年初,谭博就跟微软的 FPGA 团队合作,探索如何用 FPGA 来加速数据中心网络。谭博提出了用 FPGA 加速网络功能的设想。网络功能(Network Functions)简单地讲就是网络中的各种中间盒子(middlebox),例如防火墙、负载均衡器、加密等。这些网络功能传统上都是软件实现的,时延比较高,吞吐量比较低。FPGA 是一种可编程硬件,用它来处理网络报文,可以达到微秒级的时延、数十 Gbps 的带宽。

但问题是 FPGA 的编程很复杂,难读,难写,难调,难改。本科学计算机体系结构的时候,实验课就要求我们用 Verilog 实现一个流水线 CPU,还要求在 FPGA 上验证。当时我和郭家华一组,依托他的强大编程能力,我们肝了一个月搞出了 3000 行 Verilog 代码,但实现出来的 CPU 还有好多 bug。计算机体系结构实验课的老师是一位返聘的老先生,我们叫他 “龙芯的爸爸的爸爸”,因为龙芯之父胡伟武当年就是他的学生。老先生跟我们讲,胡伟武当年很厉害,用面包板搭数字电路,硬是做出一个像模像样的 CPU 来。老先生说我们的流水线 CPU 做得不错,可以留作下届学生的参考了。可惜,这门地狱级的实验课据说目前已经取消了。

我们这篇论文就是一个在网络领域简化 FPGA 编程的框架。当时,业界已经有很多 HLS(高层次综合)工具,可以把 C 之类的高级语言翻译成 Verilog,其中最有名的是 Vivado HLS 和 Altera OpenCL。因为我们用的是 Altera 的 FPGA 卡(Altera 现在已经被 Intel 收购),我们就用 OpenCL。那时,Altera OpenCL 的成熟度还不高,随便写一小段 C 程序,有时候编译器崩溃;有时候编译器卡死,半天出不来结果;有时候编译出来的 Verilog 执行结果是错的;有时候虽然能执行,但是性能很差,因为根本没有流水线化,全都串行执行了。

我们又没法修改 Altera OpenCL 的源码,怎么办呢?谭博指导我搞清楚怎样的操作会引发问题,怎样的操作就可以正常运行,进而找到一个可用的 OpenCL 原语子集。OpenCLMicrobench 就是我当时测试过的一小部分例子。这就更凸显出我们打算做的编程框架的意义了。用户的代码经过我们的框架编译成 Altera OpenCL,再经过 Altera OpenCL 的编译器编译成 Verilog,最后则是传统的 FPGA 综合工具。曾几何时,IE、Firefox、Chrome 等浏览器访问 DOM 元素的方式也有很大的差异,也有很多坑,jQuery 之类的框架就提供了一种统一的编程抽象来屏蔽浏览器的差异。

在 FPGA 编程中,如果一段代码里面有内存读写依赖,也就是先写后读,如果直接生成代码,那么需要等待写操作完成才能开始读操作,因为 FPGA 的内存访问一个周期无法完成,因此整个程序就没有办法流水线化。计算机体系结构中有个经典方法可以解决这个问题,也就是引入一个高速的寄存器缓存最近写入的数据,如果发现要读的数据恰好就是正在写入的数据,就从寄存器中获取最新的结果。类似这样的优化还有很多,感兴趣的可以阅读我们的论文,事实上论文中列出的优化也只是一部分。

本质上,我们的框架是提出了一个 C 语言的简单子集,不支持循环次数没有上界的循环,不支持函数递归调用,不支持指针。后来我工作后做了深度学习编译器,才知道编译学术界对这样的代码有一个学名 SCOP(Static Control Part,静态控制区域),我们 MindSpore AKG 中使用的多面体编译(polyhedral)技术也是要求代码必须是静态控制区域。在 FPGA 高层次综合中,这样的代码可以进行完全的循环展开和函数内联,变成一块不包含任何循环的代码,进而可以转换成一块组合逻辑,在合适的地方插入寄存器后,就变成一条完全流水线化的数字逻辑了。这样的数字逻辑每个时钟周期都可以接受一个输入的数据块,对数据报文的一个分片(我们称为 flit)进行处理,从而整条流水线的吞吐量就是时钟频率乘以分片大小。

在 ClickNP 的论文发表之后不久,Altera OpenCL 的新版本就能自动进行我们所做的一些优化了。这是因为这些优化很多是编译器和体系结构领域众所周知的优化,但作为一个 HLS 产品,OpenCL 也需要不断迭代,把各种优化加进去。

从 idea 到 system

一开始,我们打算把这个编程框架做成一个 C++ 库的形式。那是因为我们没想到要自己去搞这些编译优化,只是想做一层网络接口和主机通信接口的封装。但是不做编译优化,OpenCL 的性能就差到没法用。C++ 库的一个函数调用是很难进行复杂的代码变换的,也就没办法实现编译优化,因此我们只能走上自己写编译器的道路。

事实上,早在我结束研一的课程,回到 MSRA 之前,谭博就已经亲手写出了 ClickNP 的最初 1000 多行代码。这包括类似 Click 的网络功能配置文件的解析器,是用 lex 和 yacc 写的;还有主机和 FPGA 之间的通信代码;还有若干个基本的网络功能元件。我们就在这些框架代码的基础上,把整个系统开发出来。回 MSRA 前两个月,我还问谭博需要做些什么研究准备,谭博跟我说,啥都不用准备,直接来就行了。

谭博作为网络组的主管,还亲手写了这么多代码,实在是让我震惊。他今天作为大几百号人的主管,跟我们讨论项目时,也仍然很关心技术细节,甚至把电脑抢过来亲手写下了一些 API。不管是在做 ClickNP 的时候还是现在,API 的变更一定要经过评审,不能随随便便就改了。有时候我想给 ClickNP 新增一个语法用来解决眼前的问题,谭博考虑更多的是这个语法与整体的抽象是否一致,是否可以引入一个更好的抽象解决一系列的问题。而我现在作为一个小主管,就已经基本脱离代码工作,写的都是一些不合入主代码仓的 demo 代码。脱离代码一线,会导致项目的详细设计脱离轨道,API 的定义和修改过于随意,就好像盖楼我只负责做沙盘,结果建筑施工图出来跟沙盘相差甚远,功能、性能指标都缩水了。

我们主要有四位实习生参与了 ClickNP 系统的开发工作,我主要负责编译器,大四实习生彭燕庆和罗人千分别负责开发网络功能元件和应用,他们也在编译器方面帮了我很多忙;贺同负责用 Verilog 开发 FPGA 和 CPU 之间的高性能通信管道。研究员罗腊咏博士是 FPGA 的资深专家,为我们做了 Altera OpenCL 的早期探索。当然,还有微软总部 Catapult 团队的很多专业的硬件工程师,他们把网络、PCIe 等硬件能力(Hard IP)封装成了易用的接口,以数据流的形式提供给 Altera OpenCL 来使用,这是 ClickNP 能用来处理网络报文、能通过 PCIe 跟主机 CPU 通信的关键。

从 idea 到 system 并不是一件容易的事。从 7 月正式启动系统实现,到来年 1 月底正式投稿,不过半年时间。截至投稿时,代码仓一共有超过 1 万行代码、超过 2000 个 commit。虽然 MSRA 讲究 work-life balance,但在 deadline 面前,我们都把所有精力投入到系统实现中。当时异地的女朋友就跟我抱怨,每天跟她聊天的时间都不到 15 分钟。当时她的状态不太好,经常需要倾诉,我却没有投入什么时间和精力陪她。无独有偶,后来我跟阮震元一起搞 KV-Direct,他的女票就开玩笑说,我是她的情敌,因为阮震元太投入我们的 KV-Direct 了,都忘了她了。

自古忠孝难两全,work-life balance 也是说起来容易做起来难。我永远忘不了杜子德在 NOI 2009 冬令营上对我们讲的:你们这一两百人是这一届中学生里编程水平比较高的,是中国计算机未来的希望。10 年后,不管你们是在哪里,不要忘记你们身上的责任与使命。

在实现 ClickNP 的过程中,谭博总是提醒我几点:

- 聚焦。我总是思维比较发散,解决 A 问题的时候又想到了 B 问题、C 问题。这时就需要聚焦(focus),先把手头的问题解决好,再去解决其他问题,特别是那些问题可能并不在当前这个研究工作的范围内。

- 收敛。我思维发散的另一种表现是,为解决同一个问题提出了 A、B、C 三个方案却患了选择困难症,迟迟不能决定怎么做,感觉哪个方案都不够完美,按下葫芦浮起瓢。这时就需要收敛(converge),不要完美主义。首先系统地分析清楚几种方案的优劣,根据场景和需求,选定一种方案开始实现。

- 分析型思考。例如,不是把实验结果罗列出来就完事了,而是要思考结果背后的原因,并做一些额外的实验来证实或证伪自己的推测。不管是在 MSRA 还是在目前的工作中,我都发现很多人缺少分析型思考的习惯。每次到组会的时候,摆出来一些新的实验结果,就像是应付差事,跟上周讲过的结果如何对比也没有分析。

- 区分科学问题和工程问题。例如 FPGA 不能自动响应 ARP 报文,从而交换机无法自动建立三层路由规则,ClickNP 的早期版本只能做两台机器直连的实验,如果中间经过了交换机,就需要手动配置交换机的二层转发表。谭博告诉我,不要把宝贵的研究精力浪费在诸如此类的工程问题上,手动配置交换机既然能解决问题,就不要去花时间实现 FPGA 响应 ARP 报文的功能,这对我们的主要研究工作并没有帮助。

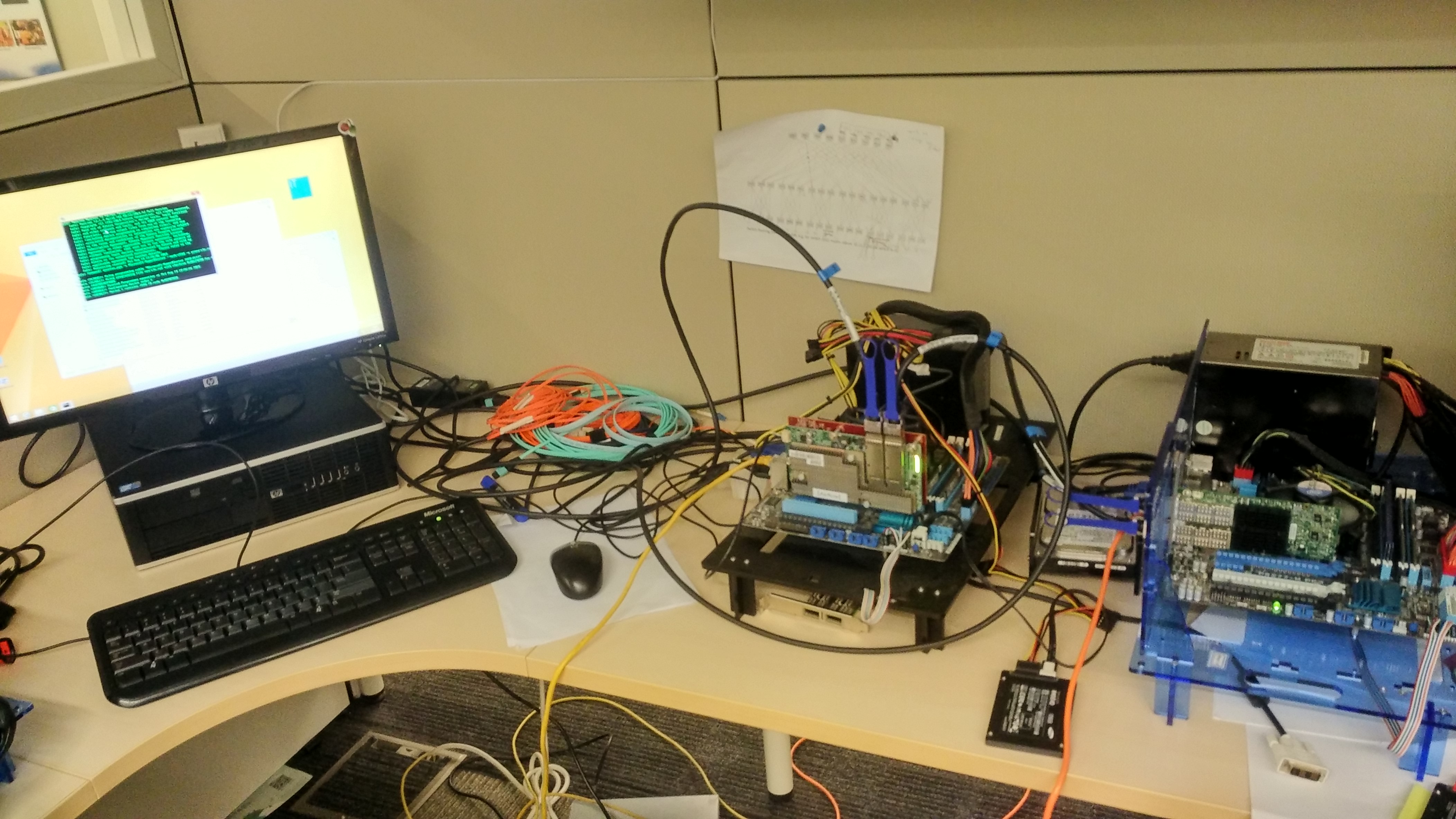

上图:摆在工位上两台主机直连的测试床,两块 FPGA 网卡之间直连

上图:摆在工位上两台主机直连的测试床,两块 FPGA 网卡之间直连

写作,完全被推倒重来

我们大概是 deadline 前 10 天才开始写论文初稿的,此时的论文初稿中只有 related work、background 等几个章节,实验也还没有做完。我们不仅要根据实验结果决定应该补做哪些实验,还需要把设计、实验部分的论文内容写出来。

我写出来的 paper 初稿基本上完全被谭博推翻重写了。作为一名初学者,我写出来的 paper 就是一篇流水账,平铺直叙地讲述系统各个组件的设计。这是不行的。据说,审稿人读完一篇文章的时间平均只有 45 分钟,并没有时间看 paper 中的每个细节,更没有时间帮一篇逻辑混乱的文章提炼核心观点、梳理逻辑。

Paper 一定要能用一句话概括出来,传递一句 key message;有几个让人眼前一亮的关键创新点,系统设计是围绕这些关键创新点展开的。 论文是非常讲究逻辑的文章,绝对不能混淆不清。审稿人也都是逻辑好手,试图在关键逻辑上瞒天过海是行不通的。有些人会列出一些并没有直接关联的 paper 作为论据来支持文章的挑战,很容易质疑 motivation(动机)是否足够。

Paper 需要是一个逻辑环环相扣的故事,首先从当前的问题引出几个关键挑战,推导出设计目标,然后是如何解决这些关键挑战的系统设计,接下来是这些系统设计对应的系统实现,最后是对这些技术创新点的实验验证。挑战、设计、实现和实验需要一一对应,切忌写了挑战但没有解决,设计了一大套精妙的机制但不知道是用来解决什么问题的,或者没有实验验证。如果有还没解决的挑战,那应该放到 future work 部分再去讲。也不宜在挑战部分提前剧透解决方案,或者在系统设计部分讲着讲着又提出一个新的挑战。

因此,很多 paper 读起来像 “八股文”。有经验的读者扫两眼就能 get 到文章的核心论点,用不了一个小时就能把文章的关键内容总结出来,这是因为什么内容该出现在什么位置,都是有讲究的,并不需要把整篇文章逐字逐句读完。如果真要把每个细节都读清楚,一篇系统 paper 大概是要花一天的时间。

有些人写 paper,经常是一个人分下来写作任务,一人写一章,写完了之后一合稿就提交,这样很容易导致逻辑混乱,因为每个人想突出的关键点不一样。因此,我们网络组写 paper 一般是先写挑战、设计和实验部分,然后再提炼核心创新点写 introduction(引言)和 abstract(摘要)。挑战、设计和实验部分也要根据全文逻辑的需要进行调整。

如何根据需要突出设计中的关键创新点?首先是要有总-分结构。例如,在章节的开头用一小节综述整个设计,表明哪一节的哪个创新点是解决哪个挑战的。也要有一张架构图与之对应。我们调研文献时,经常需要配上一张架构图,如果 paper 中没有这张架构图,就很抓狂。

其次,在描述设计的过程中记得回顾挑战,解释每个设计的目的,不要把读者想象得太聪明。读者很容易产生这样的疑惑:这个设计解决了什么问题?在方案的优缺点之间是如何权衡的?很多读者希望看到文中有这样的思辨,而不仅仅是把最终的设计结果列出来。当读者要设计一个类似的系统时,业务需求和硬件条件可能已经改变,此时的设计选择未必跟行文时的相同。这就是 KV-Direct 的审稿意见。我们的一些参数设置是依赖硬件配置的,审稿人要求我们讨论不同硬件条件下我们的方法是否还能 work,因此在KV-Direct 的终稿中我们增加了 6.3 节和 Table 5。

值得注意的是,解释设计不等于把文章写成一篇记录研究心路历程的流水账。一些同学先写研究初期提出的不成熟方案及其缺点,然后再引出真正的解决方案,希望起到 “引人入胜” 的效果。但这样容易导致审稿人困惑,因为不是每个审稿人都有时间逐字逐句地阅读论文,去理解其中弯弯绕的逻辑。我的浅见是,论文不是小说,逻辑以简单直接为宜。

在写 related work 的时候,我发现一篇十年前把 Click 编译到 FPGA 的工作,如临大敌,这岂不是跟我们做的一样?谭博却不慌不忙地教诲我:太阳底下没有新鲜事。如果你发现一篇文章特别新,那大概只能说明你对相关工作还不够了解。 相比那篇工作,网络的性能提升了一个数量级,编译中要解决的挑战多多了,因此我们提出的编程框架是为 FPGA HLS 深度优化的,而不是不顾性能地直接把 C 代码扔进编译器;而且我们还支持 FPGA 和主机之间通信。

从投稿到中稿

在 deadline 前三四天,我们一起熬了好几个夜,其中最后两天连续工作了 44 个小时,谭博也跟着我们一起熬夜。这似乎成了我们组的惯例,每篇 paper 都是提前两周才动笔开始写,搞得非常紧张;不管 paper 准备得怎么样了,是否能赶上 deadline,大家总是要一起熬几夜。

对于这篇 paper,谭博觉得信心满满,“如果这都中不了,我都不知道什么样的 paper 能中 SIGCOMM 了”。FPGA 在数据中心的应用是一个热门的研究领域,这篇 paper 又是微软公开发表的第一篇 FPGA 在网络领域的论文,有很强的时效性。同时,这也是第一个使用高级语言在 FPGA 上编程实现网络功能,并达到 40 Gbps 的高性能编程框架。

上图:ClickNP 论文的审稿评分

上图:ClickNP 论文的审稿评分

2016 年 4 月 26 日,我们 paper 的录用通知下来了,女朋友却提出分手了,因此那个时候真的是悲喜交加。一般我们组里有人中了 paper,都是要请大家吃饭的。但因为我的心情不好,就没有请大家吃饭,也因此非常对不起大家。

当时,会议主席还联系我们,说我们的 paper 选成了 experience track 了,但是文章看起来是 research track 的,就按照 research track 的流程来评审了,要求我们修改 track,否则不予录用。谭博很吃惊,为什么 track 会选错。我当时也不懂这两个 track 的区别,在投稿的时候就发现勾上了 experience track 那个选项,但是没有提出来,还以为是谭博选的。谭博赶紧给会议主席回了一封信来澄清。谭博跟我说,如果发现了可能的问题,一定要提出来,不要自作主张,否则如果会议主席没有好心把 track 给切过来,就吃了哑巴亏。

从收到录用通知到提交 camera ready(最终)版本的时间只有几周,我们需要把审稿人的意见整理出来,进行回复;按照审稿人的意见进行修改,先提交修改版初稿;审稿人再次提出修改意见,最后提交终稿。提交修改版初稿的那几天,我正在学校处理分手的事情,好在修改 camera ready 的过程不太需要创造力。我一开始修改的时候对审稿意见言听计从,其中一个审稿意见认为我们并不是 “第一个” 用高级语言在 FPGA 上实现网络功能的编程框架。但谭博认为我们仍然应该保留某种形式的 “第一个”,从而在最终版本中增加了 “达到 40 Gbps 性能” 的限定词。

第一次坐飞机,第一次出国

当年的 SIGCOMM 会议恰好跟奥运会都在巴西。就在 SIGCOMM 会议召开前的几个月,巴西爆发了寨卡病毒疫情,大家都不敢去巴西了,特别是微软的很多研究员,都决定不去参加这届的 SIGCOMM。SIGCOMM 主办方也感受到了这种担忧,把会议举办地从大城市 Salvador(萨尔瓦多)改到了岛上的城市 Florianopolis,因为这里的人口密度更低,气温也相对更低,蚊子相对较少(寨卡病毒主要是通过蚊子传播的)。

当年,虽然国内能在 SIGCOMM 上发表长文的人不多,但还是有不少高校和企业去 SIGCOMM 上观摩,以及参与 Poster 和 session。例如,清华和华为都派出了超过 10 个人参加当年的 SIGCOMM。因为当时微软没有人跟我一起去开会,我就跟清华的张宇超一起去,请她通过学校帮我订了机票,往返费用高达 18000 多元。

说来有趣,那竟然是我一生中第一次出国(境),第一次坐飞机,第一次坐飞机就是长达 40 多个小时、从欧洲转机到南美洲的长途旅行。在里约热内卢机场转机的时候,奥运闭幕式即将举行,随处可见荷枪实弹的宪兵在巡逻,因为前些天就发生过枪击案。

自那次起,我也发现我对时差和气压差容忍度很强,去了以后睡了一大觉就倒过来时差了,飞机起飞和降落的时候耳朵几乎没有感觉。对时差不敏感,可能跟我博士期间生活不规律有关,经常中午甚至下午才起床,但如果需要上午起来开会也是可以的。直到今天,我工作日上午需要八点多起床去上班,依靠闹钟把我叫醒;但到了周末,还是会一觉睡到十一二点。

上图:沙滩上的时间印迹

上图:沙滩上的时间印迹 上图:沙滩上的我(感谢张宇超摄影)

上图:沙滩上的我(感谢张宇超摄影) 上图:沙滩小路上的涂鸦

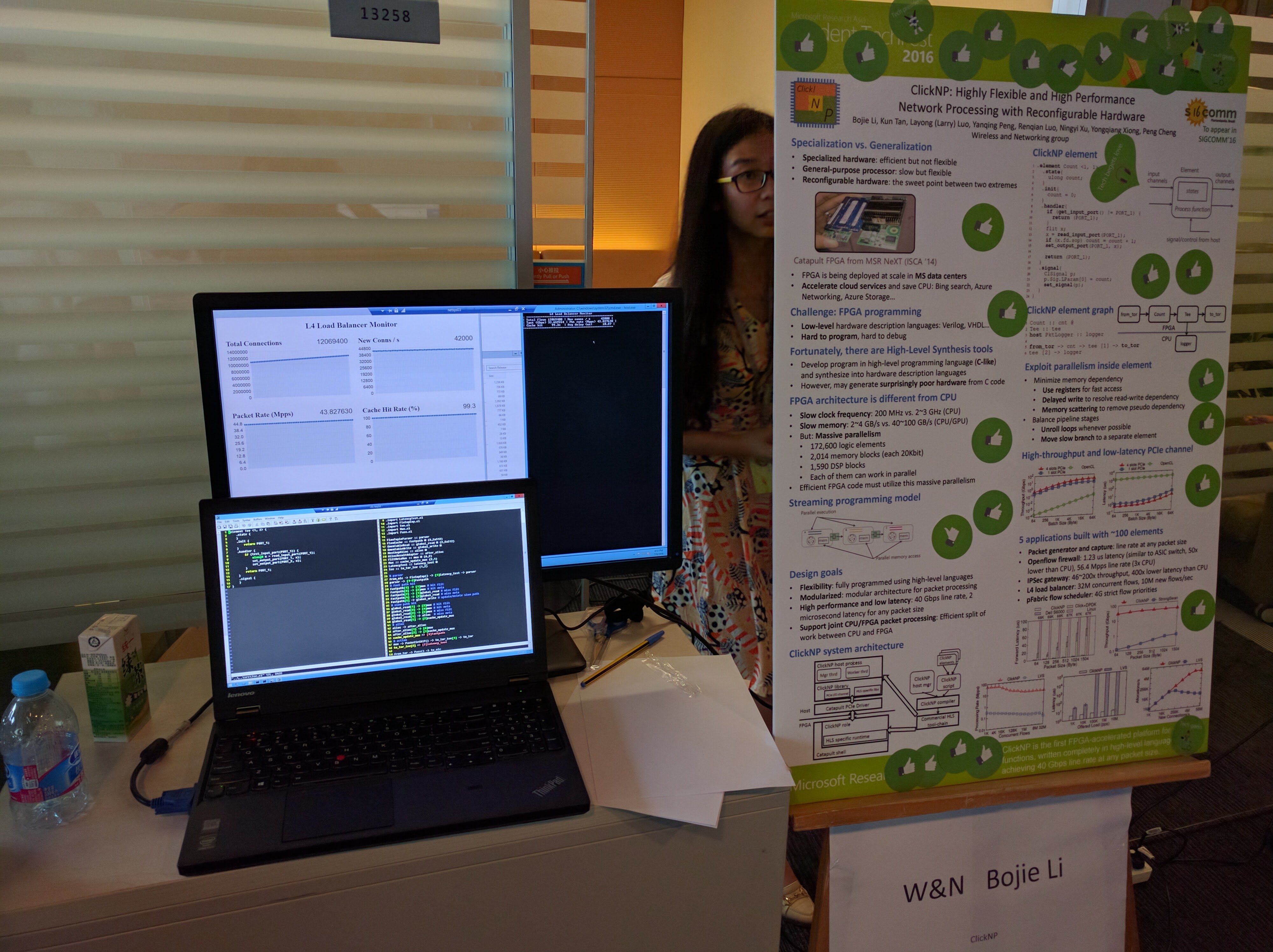

上图:沙滩小路上的涂鸦 上图:SIGCOMM 2016 展示 demo

上图:SIGCOMM 2016 展示 demo 上图:SIGCOMM 2016 展示四层负载均衡器的 demo,用 NW.js 做了一个简单的 GUI

上图:SIGCOMM 2016 展示四层负载均衡器的 demo,用 NW.js 做了一个简单的 GUI 上图:欢迎晚宴

上图:欢迎晚宴

当时我们为了防止感染寨卡病毒,带上了各种驱蚊措施,包括驱蚊手环、驱蚊水,进了房间第一件事就是像侦探一样找蚊子。不过,我们开了一周的会,似乎也没见到几个蚊子的踪影。

第一次参加学术会议,我还是很认真的,会后写了《网络技术的风向标——SIGCOMM 2016》,还被 MSRA 官方的公众号发表了。在第二篇 paper KV-Direct 在 SOSP 2017 上发表之后,我也写了《SOSP:计算机系统研究的风向标》,同样发表于 MSRA 官方公众号。后来,越来越多的国内高校也开始系统地总结参会记录,例如上海交大 IPADS 研究所每次都会派学生和老师参加系统领域顶会,并对每个工作都做很好的总结。

ClickNP 在公司内也有比较大的影响力。我在 MSRA Student Techfest 上演示了已经中稿但尚未正式发表的 ClickNP。洪院长走过来,饶有兴趣地在展位前停留了两分钟,问了我好几个很好的问题。洪院长说,他还是第一次看到 ClickNP 的演示,感觉效果不错。ClickNP 也获得了当年的最佳演示奖(best presentation award)。

上图:在 MSRA Student Techfest 上展示 ClickNP

上图:在 MSRA Student Techfest 上展示 ClickNP

上图:在 MSRA Student Techfest 上向洪院长展示 ClickNP

上图:在 MSRA Student Techfest 上向洪院长展示 ClickNP

ClickNP 这个项目没有开源,一直是在我们网络研究组内部使用。虽然它孵化了 MP-RDMA、KV-Direct、MELO 等多个后续工作,但外人所知的仅仅是一篇 paper。目前这篇 paper 已经有 279 个引用(2023 年 1 月 23 日 Google Scholar 数据),已经给可编程网卡领域的研究者很多启发了,但它的代码却被尘封在服务器里。这是我在 MSRA 最大的遗憾。我希望所做的东西能够被成千上万人使用,就像当年在 LUG 做的网络服务一样。

聚是一团火,散作满天星

罗人千是比我低两届的 MSRA 和中科大联合培养学生。做完 ClickNP 这个项目后,人千就说再也不想做 FPGA 了。看来,FPGA 的难写、难调、难改还是蛮有杀伤力的。当他结束研一在校的一年,再次回到 MSRA 的时候,联合培养的方向就从网络转到了 AI。人千博士毕业后留在了 MSRA,成为一名研究员,目前 Google Scholar 的总引用数比我还多。

彭燕庆也比我低两届,是上海交大 ACM 班来 MSRA 做大四一年实习的。他本科毕业后去了犹他州立大学读博,也不再做网络了,而是研究数据库方向,也产出了多篇优秀的 paper,目前就职于 Meta。

贺同在我们这个项目中实习后,申请到了 UCLA 的硕士,目前就职于 Google。

罗腊咏博士在做完我们这个项目后,一直在用 FPGA 加速网络领域深耕,目前也在国内互联网公司中担任资深技术专家。

徐宁仪博士作为资深的 FPGA 专家和硬件研究组的主管,在 ClickNP 项目中指导我们设计了整体的硬件架构,后来一直致力于 AI 硬件体系结构的研究,目前在上海交通大学清源研究院担任教授。

加上继续坚守 MSRA 的熊勇强老师和程鹏博士,在华为的谭博和我,以及我的校内导师陈恩红教授,我们 10 位主要参与者当时就来自 5 个不同的单位(4 个学校),现在分属 7 个单位,真是:聚是一团火,散作满天星。在后文中,我们还将看到更多老师、朋友和大神,真可谓:海内存知己,天涯若比邻。

本文是《MSRA 读博五年》系列文章(一)从小白到第一篇 SIGCOMM,未完待续……